# Design-Space Exploration for CMOS Photonic Processor Networks

Vladimir Stojanović<sup>1</sup>, Ajay Joshi<sup>2</sup>, Cristopher Batten<sup>3</sup>, Yong-Jin Kwon<sup>4</sup>, Scott Beamer<sup>4</sup>, Sun Chen<sup>1</sup> and Krste Asanović<sup>4</sup>

<sup>1</sup>MIT, <sup>2</sup>Boston University, <sup>3</sup>Cornell University, <sup>4</sup>UC Berkeley

## Acknowledgments

- Rajeev Ram, Milos Popovic, Franz Kaertner, Judy Hoyt, Henry Smith, Erich Ippen

- Hanqin Li, Charles Holzwarth

- Jason Orcutt, Anatoly Khilo, Ben Moss, Jie Sun, Jonathan Leu, Michael Georgas, Imran Shamim

- Dr. Jag Shah DARPA MTO

- Texas Instruments

- Intel Corporation

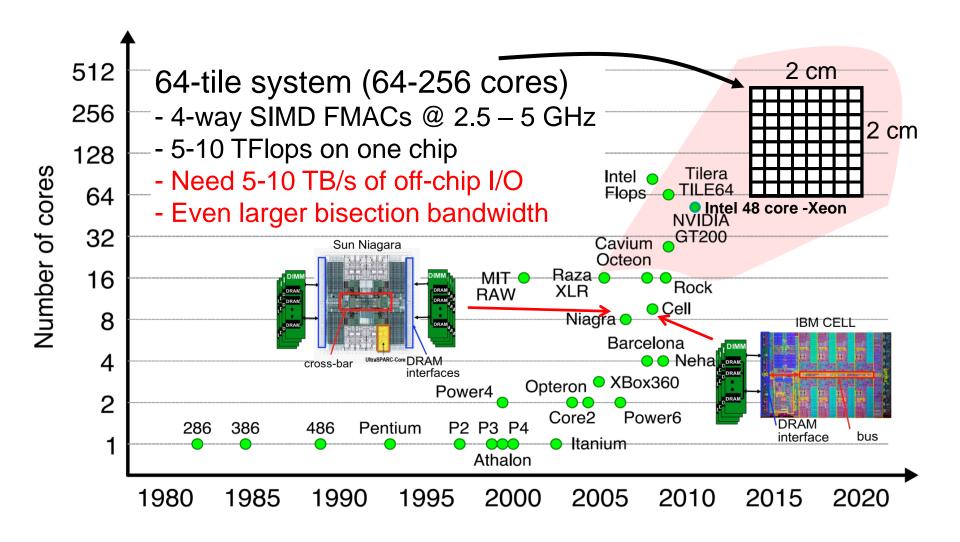

## Processors scaling to manycore systems

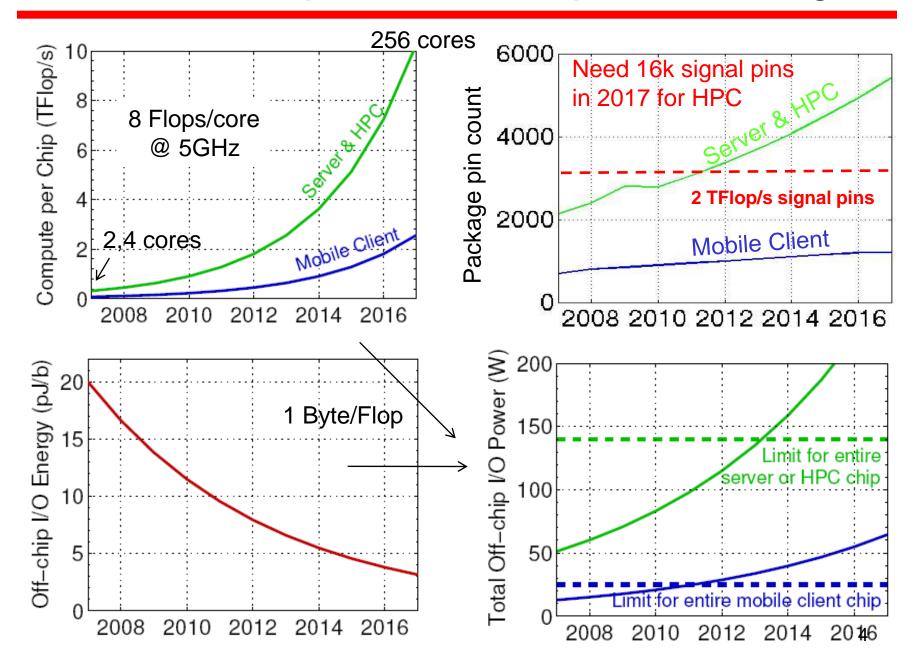

## Bandwidth, pin count and power scaling

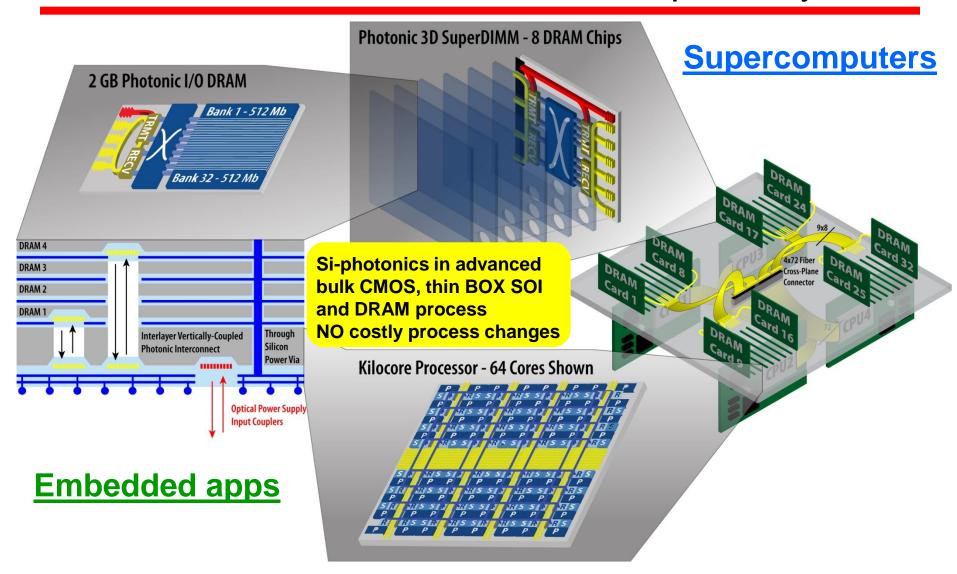

#### Monolithic CMOS-Photonics in Computer Systems

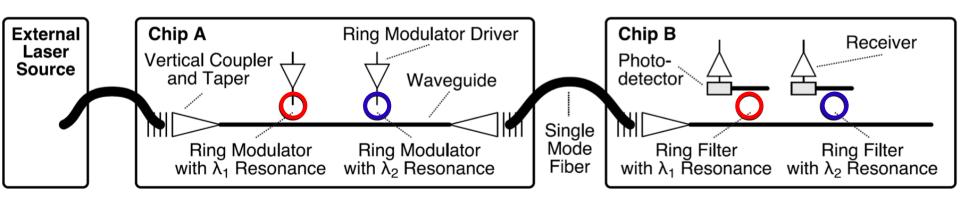

Bandwidth density – need dense WDM Energy-efficiency – need monolithic integration

## CMOS photonics density and energy advantage

| Metric                                            | Energy<br>(pJ/b) | Bandwidth<br>density (Gb/s/µ) |

|---------------------------------------------------|------------------|-------------------------------|

| Global on-chip photonic link                      | 0.25             | 160-320                       |

| Global on-chip optimally repeated electrical link | 1                | 5                             |

| Off-chip photonic link (100 µ coupler pitch)      | 0.25             | 6-13                          |

| Off-chip electrical SERDES (100 µ pitch)          | 5                | 0.1                           |

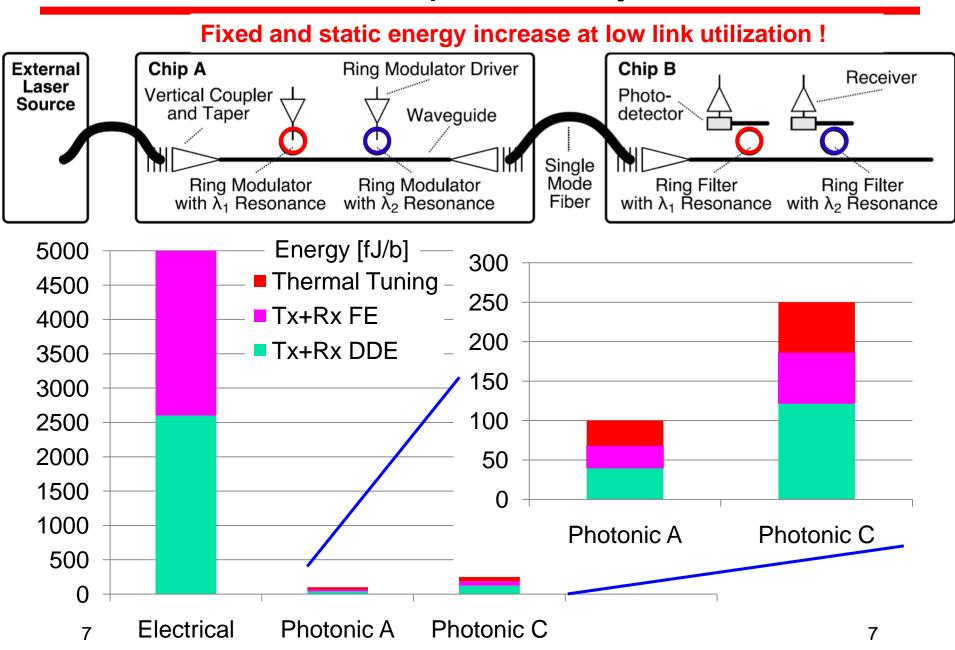

## But, need to keep links fully utilized ...

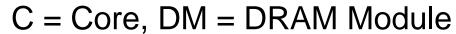

# Core-to-Memory network: Electrical baseline

Both cross-chip and I/O costly

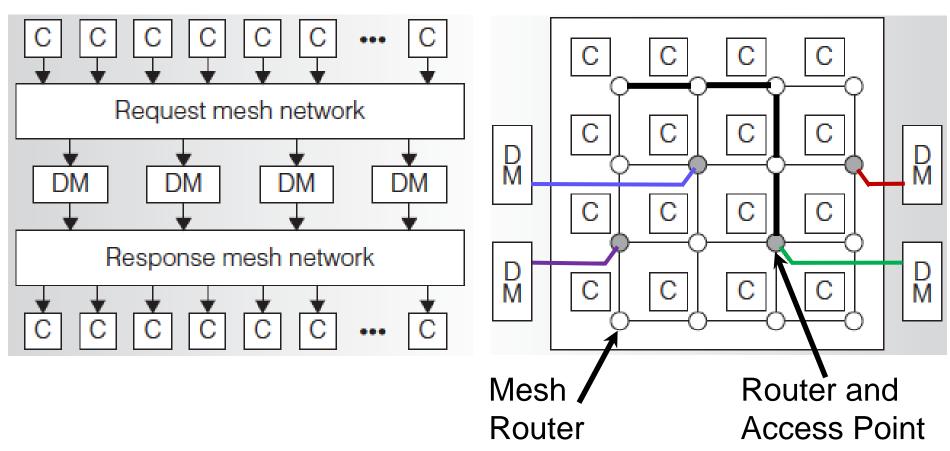

# Aggregation with Optical LMGS\* network

\* Local Meshes to Global Switches

- Ci = Core in Group i, DM = DRAM Module, S = Crossbar switch

- Shorten cross-chip electrical

- Photonic both part cross-chip and off-chip

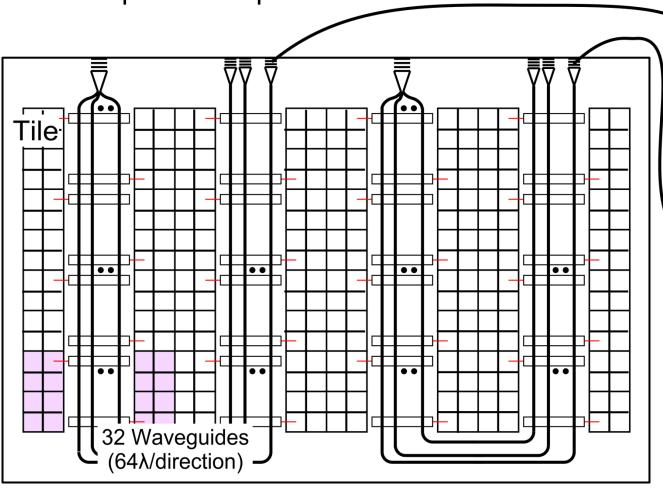

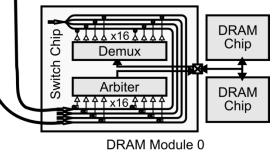

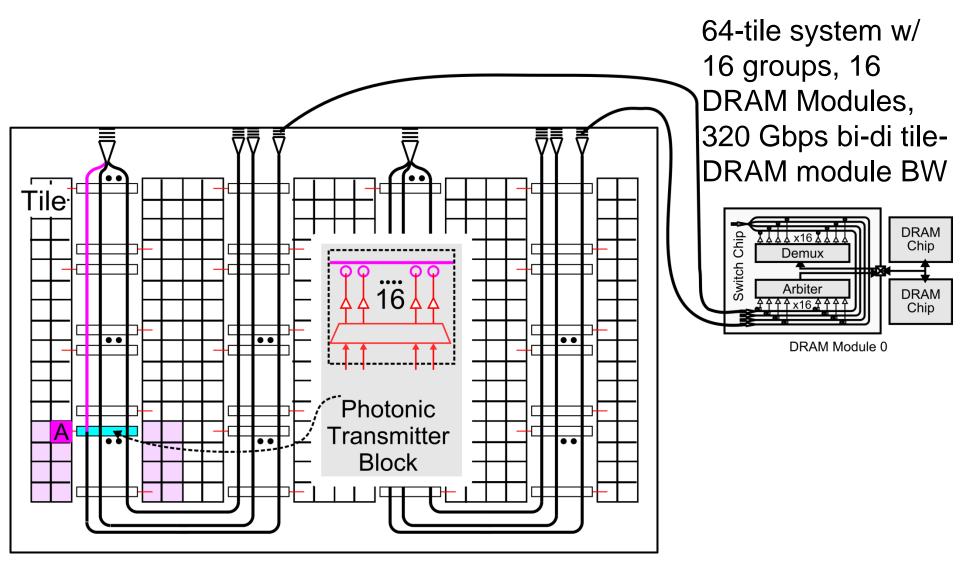

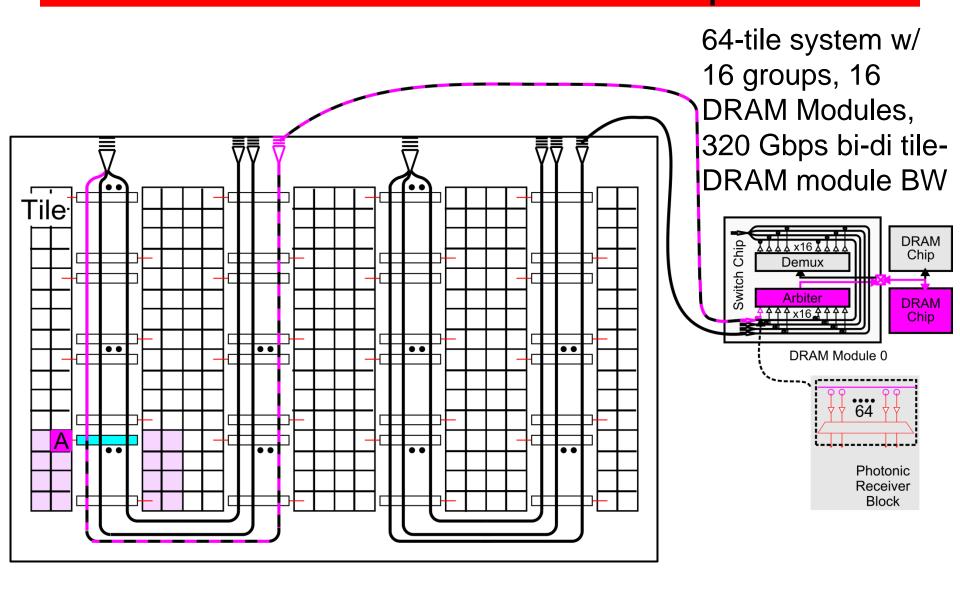

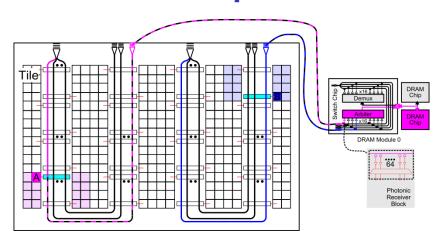

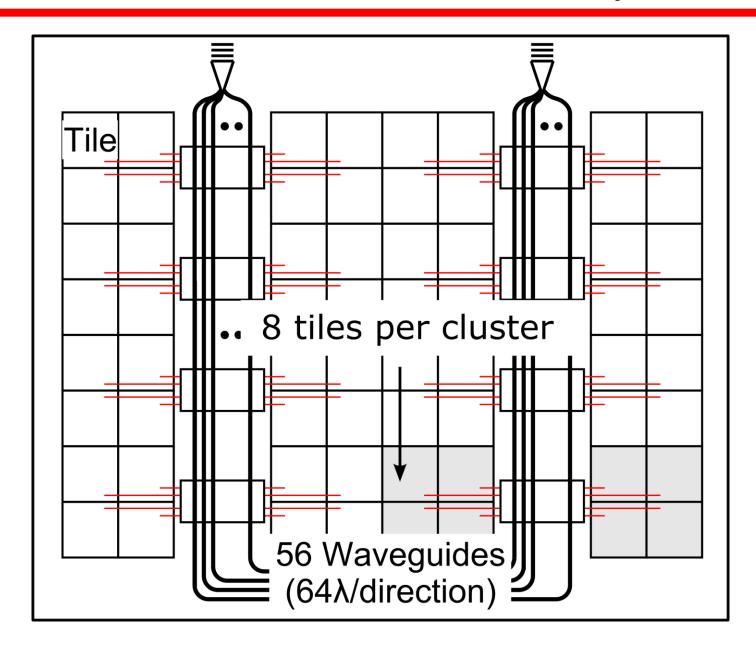

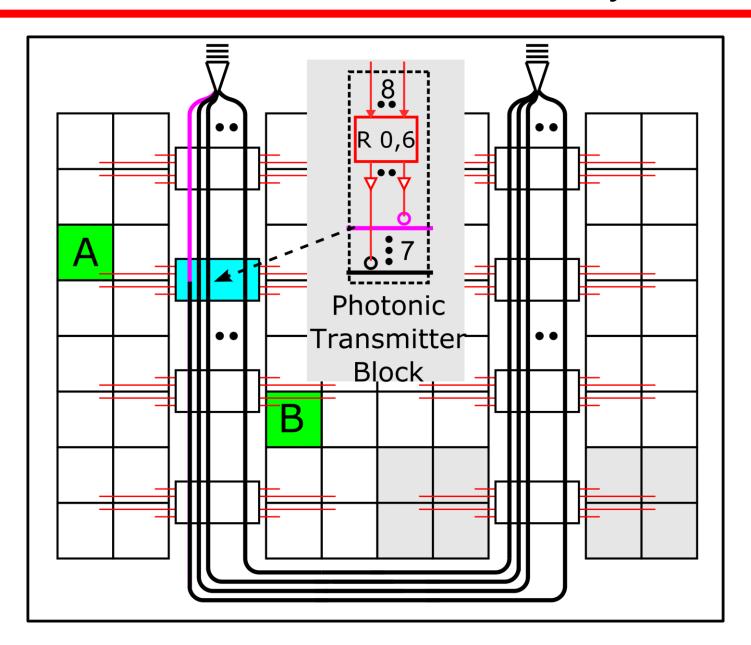

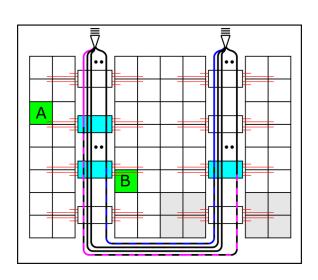

## Photonic LMGS: Physical Mapping

Network layout optimization significantly affects the component requirements

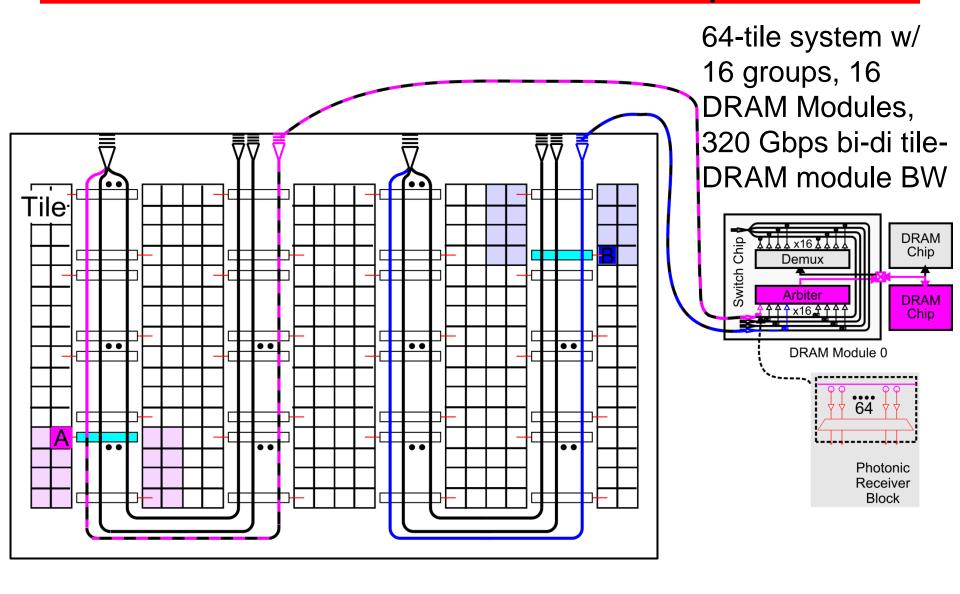

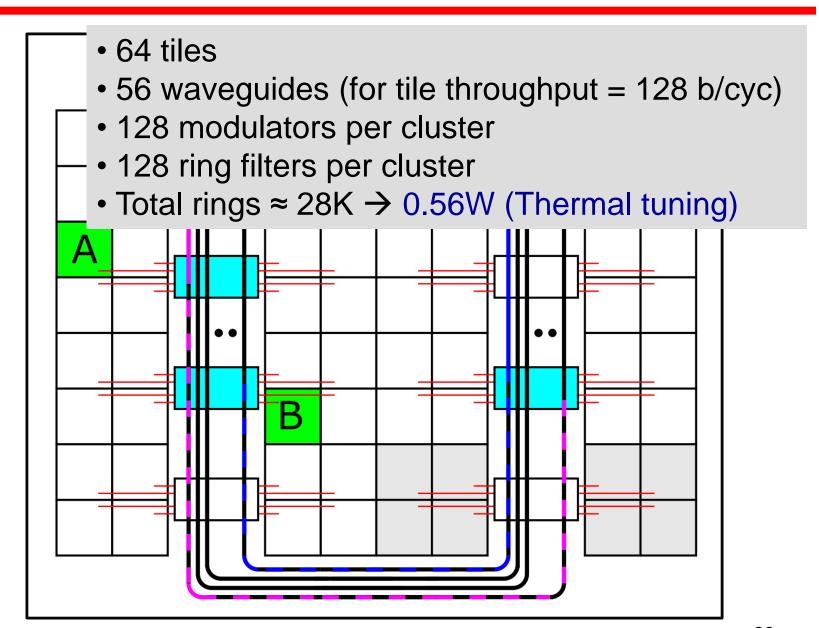

64-tile system w/

16 groups, 16

DRAM Modules,

320 Gbps bi-di tileDRAM module BW

- 64 tiles

- 64 waveguides (for tile throughput = 128 b/cyc)

- 256 modulators per group

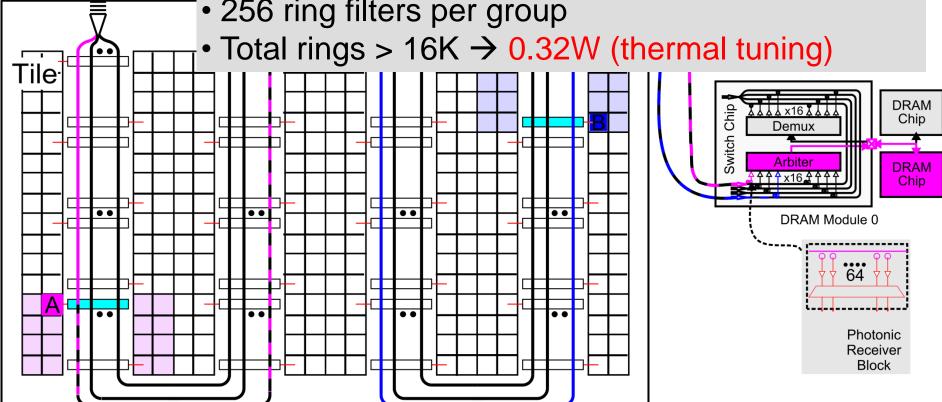

- 256 ring filters per group

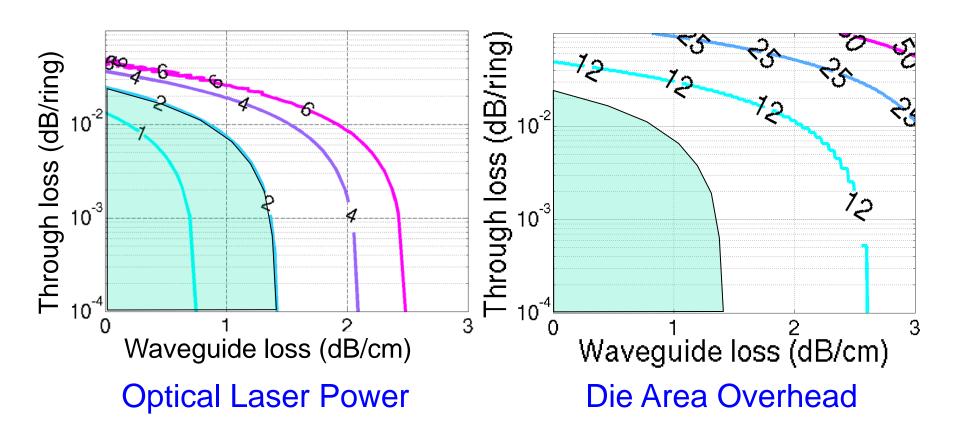

## Photonic device requirements in LMGS - U-shape

Waveguide loss and Through loss limits for 2 W optical laser power

## Photonic LMGS – ring matrix vs u-shape

#### **LMGS** – ring matrix

#### LMGS - u-shape

- 0.64 W power for thermal tuning circuits

- 2 W optical laser power

- Waveguide loss < 0.2 dB/cm</li>

- Through loss < 0.002 dB/ring</li>

- 0.32 W power for thermal tuning circuits

- 2 W optical laser power

- Waveguide loss < 1.5 dB/cm</li>

- Through loss < 0.02 dB/ring</li>

[Batten et al – Micro 2009]

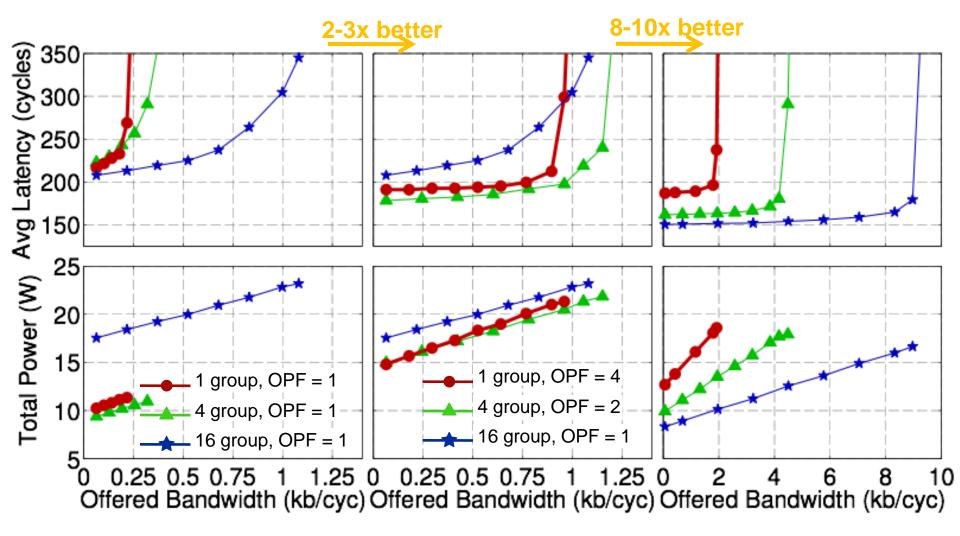

#### Power-bandwidth tradeoff

Electrical with grouping

Electrical with grouping and over-provisioning

Optical with grouping and over-provisioning

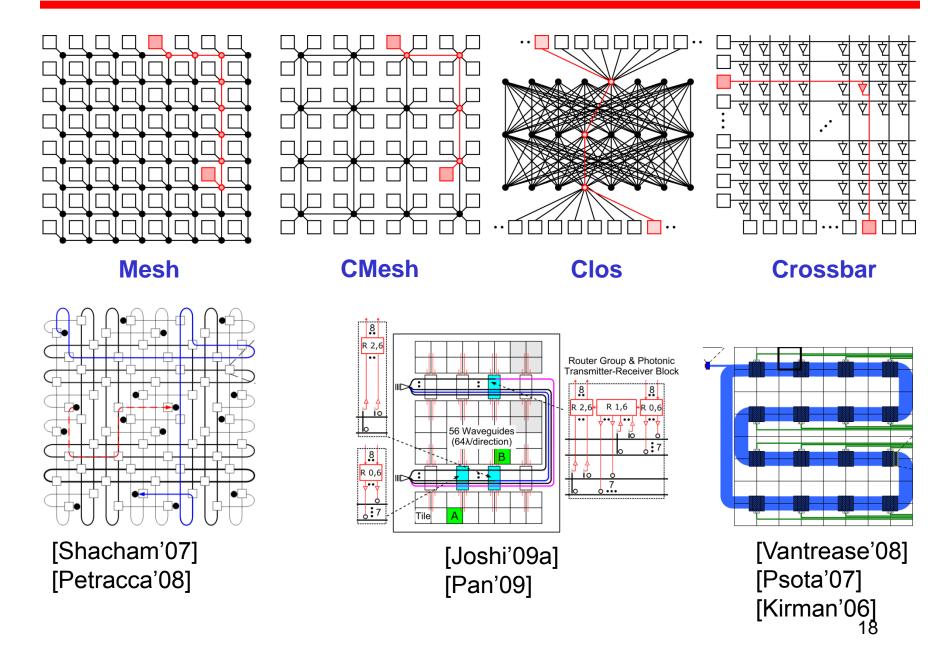

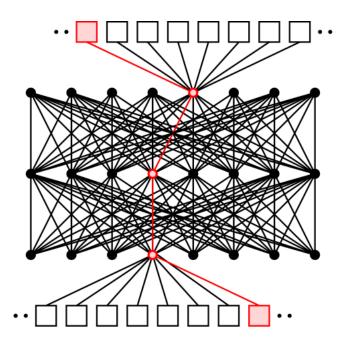

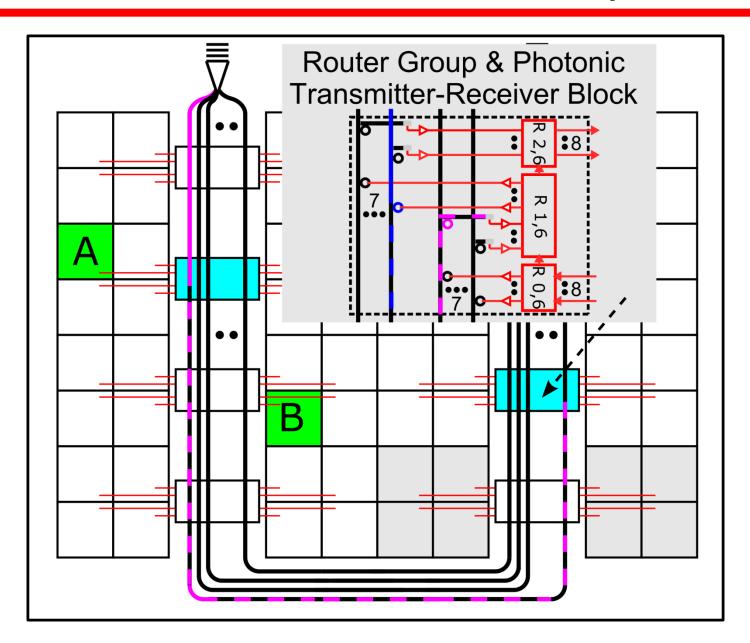

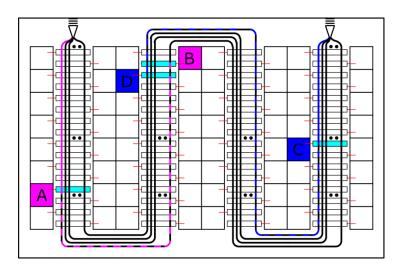

## Landscape of on-chip photonic networks

#### Clos with electrical interconnects

#### 8-ary 3-stage Clos

Physical mapping

- Two 8 x 8 Routers

- Eight 8 x 8 Routers

#### Logical topology

- 10-15 mm channels

- Pipelined Repeaters

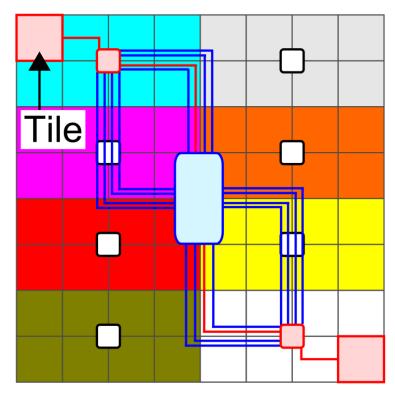

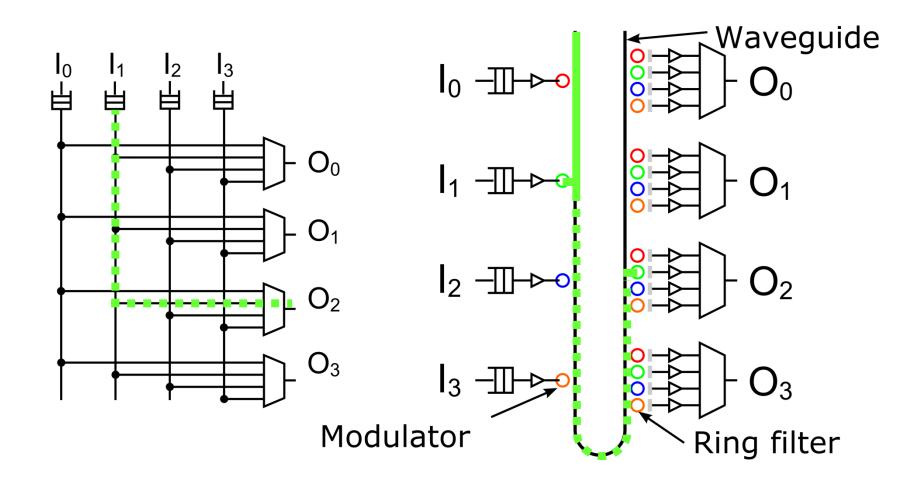

# Centralized Multiplexer Crossbar

**Electrical design**

**Photonic design**

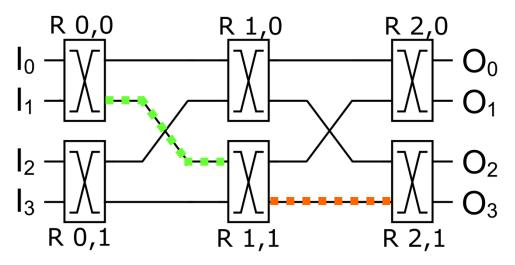

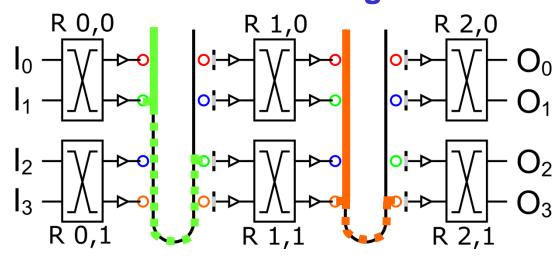

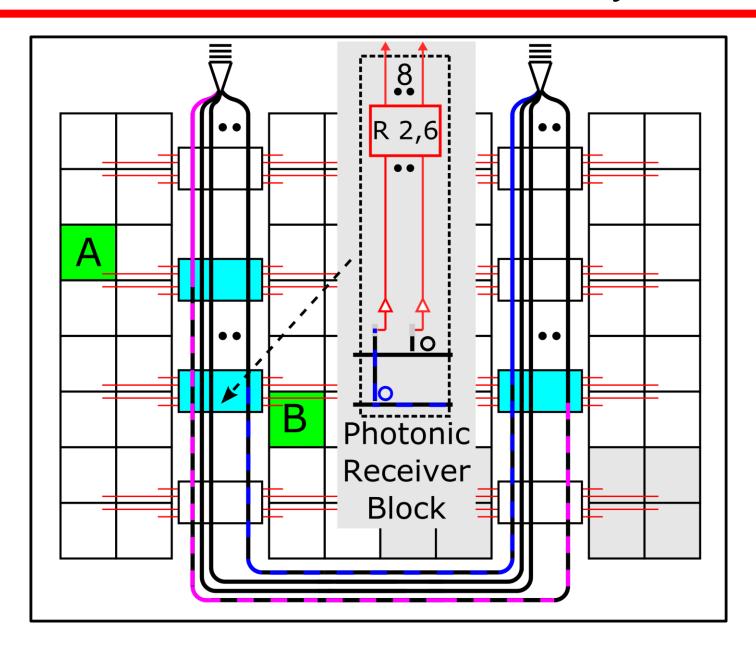

## Clos network using point-to-point channels

#### **Electrical design**

**Photonic design**

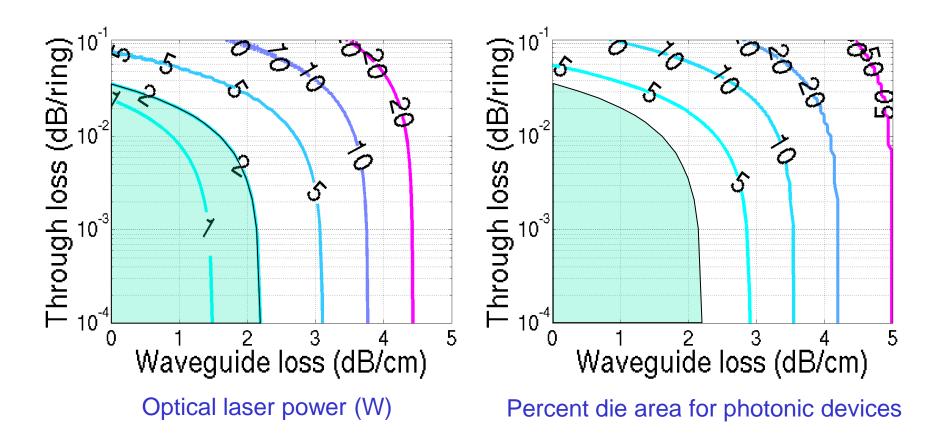

#### Photonic device requirements in a Clos

Waveguide loss and Through loss limits for 2 W optical laser power constraint

## Photonic device requirements in a Clos

2 W optical power contours

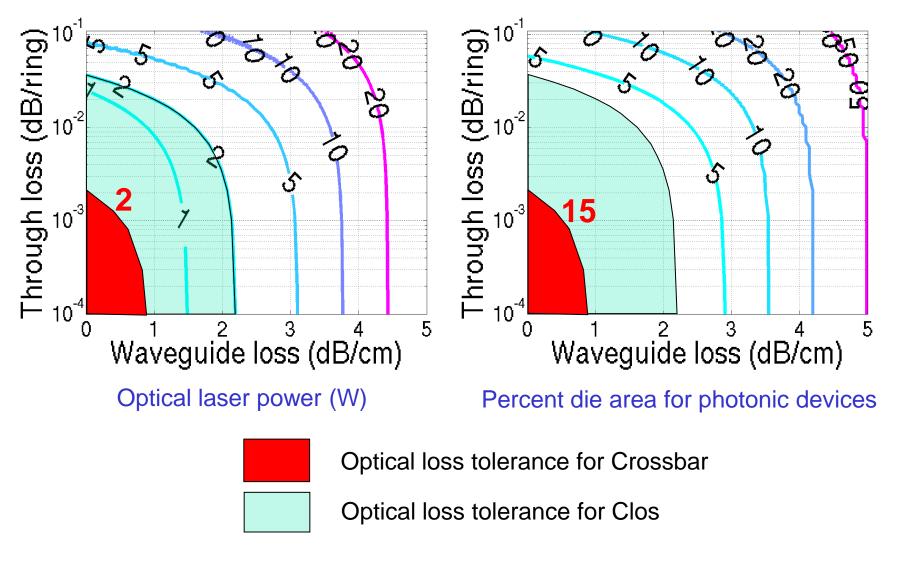

#### Photonic Crossbar vs Photonic Clos

#### Crossbar

#### Clos

- 10 W power for thermal tuning circuits

- - Waveguide loss < 1 dB/cm</li>

- Through loss < 0.002 dB/ring

- 0.56 W power for thermal tuning circuits

- For 2 W optical laser power For 2 W optical laser power

- Waveguide loss < 2dB/cm</li>

- Through loss < 0.05 dB/ring</li>

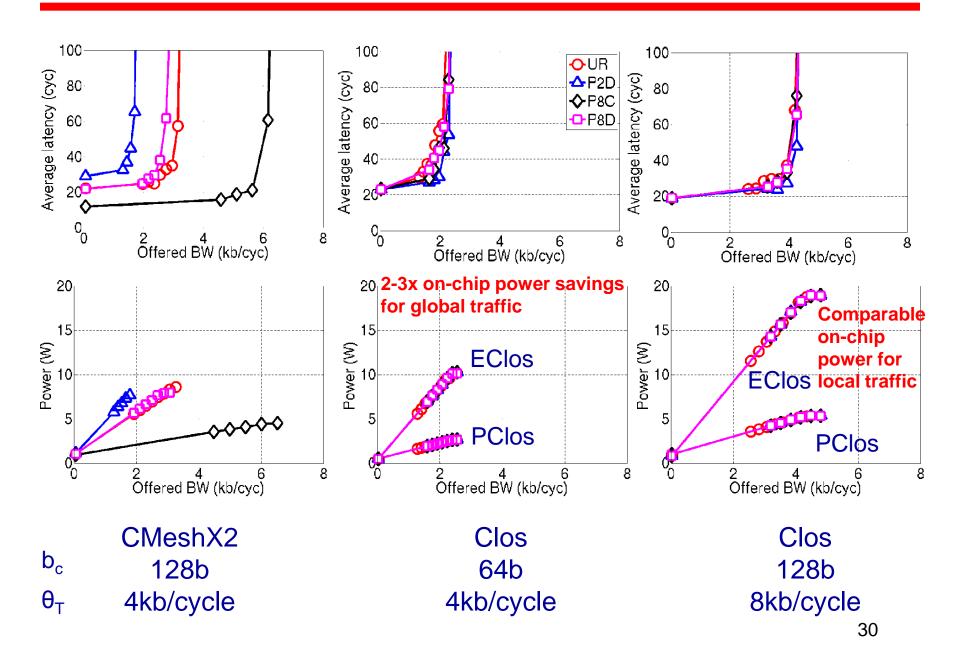

#### Power-Bandwidth tradeoff

#### Conclusion

- Computer interconnects are very complex microcommunication systems

- Cross-layer design approach is needed to solve the on-chip and off-chip interconnect problem

- Most important metrics

- Bandwidth-density (Gb/s/um)

- Energy-efficiency (mW/Gb/s)

- Monolithic CMOS-photonics can improve the throughput by 10-20x

- But, need to be careful

- Optimize network design (electrical switching, optical transport)

- Use aggregation to increase link utilizations

- Optimize physical mapping (layout) for low optical insertion loss