Pritpal S. Kanhaiya, Gage Hills, Dimitri A. Antoniadis, and Max M. Shulaker

DOI: 10.1109/LED.2018.2851191

Abstract:

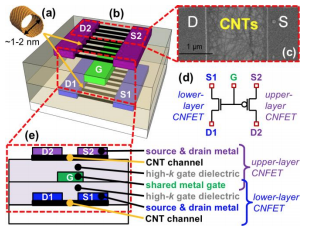

We experimentally demonstrate a three-dimensional (3D) field-effect transistor (FET) architecture leveraging emerging nanomaterials: Dual Independent Stacked Channel FET (DISC-FET). DISC-FET is comprised of two FET channels vertically integrated on separate circuit layers separated by a shared gate. This gate modulates the conductance of both FET channels simultaneously, although the stacked channels are independent, i.e., n‑type or p‑type with separate source and drain terminals separately accessed via routing. This 3D FET architecture enables new opportunities for area-efficient 3D circuit layouts. The key to enabling DISC-FET is low temperature processing to avoid damaging lower-layer circuits during upper-layer circuit fabrication. As a case study, we use carbon nanotube (CNT) FETs (CNFETs) since they can be fabricated at low temperature (e.g., <250 °C). We demonstrate wafer-scale CMOS CNFET-based digital logic circuits: 2‑input “not-or” (NOR2) logic gates designed using DISC-FETs with independent NMOS CNT channels below and PMOS CNT channels above a shared gate. Our NOR2 gates achieve: 1) average output voltage (VOUT) range of 94% of the supply voltage (VDD) for input voltage (VIN) ranging from 0 V to VDD. 2) output gain (maximum value of ‑ΔVOUT/ΔVIN) of 6.3. 3) logic gate-level hysteresis of 2.4% VDD, measured as the difference in VIN at which VOUT = VDD/2 between forward and reverse sweeps of VIN. All statistics are averaged over 500 NOR2 gates measured with VDD = 1 V. This work highlights the potential of 3D integration not only for enabling new 3D system architectures, but also new 3D FET architectures and 3D circuit layouts.